Science/Research 詳細

カリフォルニア大学バークリー校、最大規模のSiフォトニックスイッチ

May, 7, 2015, Washington--カリフォルニア大学バークリー校の研究チームは、新しいシリコンフォトニックスイッチを開発した。これはこれまでに報告された中で最大規模であり、最小エネルギー損失スイッチ。スイッチング速度はサブマイクロ秒、数100nmの広帯域スイッチである。

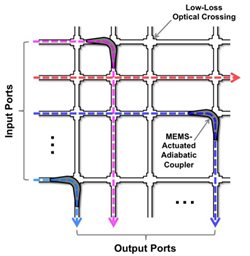

同大学集積フォトニクス研究所ポスドク研究者、Tai Joon Seok氏によると、この光スイッチは50入力、50出力チャネルを持ち、2500のスイッチング素子がこれらのチャネルのクロスポイントに存在する過去最大規模のシリコンフォトニックスイッチである(過去の最大規模Si光スイッチは8×8)。また、このスイッチは、1×1㎝以下のシリコンチップにコンパクトに集積できる。

ネットワークでの光スイッチの役割

光通信ネットワークでは、光スイッチは集積光回路を透光信号のパスを再構成し、信号が一つの回路から別の回路に選択的にスイッチされるようにする。スイッチ規模の大きな制限要因は、スイッチアーキテクチャによって生ずる累積光損失。Seok氏によると、この新しいブレイクスルーは大きい。光スイッチの規模、入出力チャネルの数を増やすことでネットワークが処理する光信号の容量が大きくなるからだ。

普通のシリコンフォトニックスイッチは、光素子としての1または2入力と出力チャネル(1×2、2×2)の小さな光スイッチを多数集めて較正されている。このような素子を相互にカスケードして2Dスイッチングネットワークを形成する。光信号がそのネットワークを通るとき、光信号が多数のスイッチング素子を通過するにともないエネルギー損失が累積する。このスイッチング素子は光エネルギーの100%を通過させることはできないので、スイッチのサイズに制限がある。

「一般に光すねるギーロス、つまり光挿入損失は、スイッチのスケールがマスにつれて急速に増える。その損失を補償するめために光アンプが必要になるが、これはスイッチの消費電力を増やす。これはスイッチあたりの全般的な価格増となる」。

この問題に対処するために、研究チームはスケーラビリティが可能になる新しいスイッチアーキテクチャを設計した。小さな光スイッチを連続的に接続してスイッチングネットワークを構成するのではなく、新しいアーキテクチャはMEMSスイッチング機構を持つシングルステージスイッチであり、累積損失という問題を完全に払拭している。

Seok氏によると、研究チームは先ずボトムSiレイヤーを形成してイーストからウエストへの入力、ノースからサウスへの出力チャネルを作製した。次に、犠牲スペーサ層の助けを借りて、上位のSiレイヤーを構築・形成して、断熱カプラ(adiabatic coupler)という特殊タイプスイッチングエレメントを作製した。断熱カプラは徐々にテーパ状になる導波路で、これによって光は一つのチャネルから別のチャネルに波長無依存で転送される。

スイッチが「ON」モードの時、トップレイヤーの断熱カプラがボトムチャネルに引き下ろされ、光を転送し、入力チャネルから出力チャネルへ90°曲げられている。スイッチが「OFF」モードの時、光は入力チャネルに留まり、スイッチングエレメントの影響を受けない。これは、トップとボトムのレイヤー間に距離があるためである。

「このアーキテクチャでは、各入力ポートからの光は光パスの1つのスイッチングエレメントしか通らない。従来のSiスイッチのように多数のエレメントを通らないので、エネルギー損失が大きくなることはない」とSeok氏は説明している。

さらに、「スイッチオフ」モードでは、ボトムレイヤーチャネルの光伝搬はチャネル内に留まり、スイッチングエレメントからの擾乱を受けることがないので、エネルギー損失が低下する。その結果、新規デザインのスイッチのポートあたりのエネルギー損失は従来のスイッチよりも3倍少ない。

Seok氏によると、新しいスイッチアーキテクチャは極めてスケーラブルであり、微小チップで100×100ポートを越えるスイッチが作製可能である。また、新デザインのスイッチは数100nm帯域を特徴としており、これは普通のシリコンスイッチの帯域と比べると約10倍広帯域であり、情報処理ネットワークが大容量化できる。

「3D-MEMS光スイッチのような市販のデバイスは入出力ポートが最大数100ポートあり、低エネルギー損失であるが、そのようなスイッチの速度は遅く、ミリ秒レベルであり、物理的サイズも大きい」(Seok氏)。

新開発のスイッチは、サブマイクロ秒のスイッチングタイムを特徴としており、これは3D-メススイッチよりも3桁高速である。また、このスイッチはシリコンフォトニクスベースであるので、1×1㎝以下の微小なシリコンチップに実装でき、製造コスト削減、ローコスト量産を可能にする。