Science/Research 詳細

低消費電力AIを実現するシリコン光回路を従来比17分の1のサイズにコンパクト化

May, 17, 2023, ふじみ野--KDDI総合研究所と学校法人早稲田大学は、AIの低消費電力化と高速化の実現を目指し、従来比で約17分の1の面積の光AIアクセラレータ用シリコン光回路を試作し、時系列データの予測を行うことに成功した。

回路面積縮小の工夫

これまで研究されてきたシリコン上に形成した光回路では、AIのモデルの一つであるリザバーコンピューティングを動作させるために、現在の情報と過去の情報を混ぜ合わせる必要があり、以下のいずれかの構造を採用していた。

1.信号をネットワーク状に形成された光回路で何度も混ぜ合わせる構造

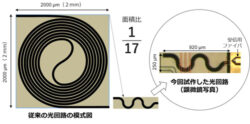

現在の情報と過去の情報が効果的に混ざるようなタイミングとするためにネットワークの節間の距離を確保する必要があり、素子面積が広くなる(16mm2)。ニューロン数(神経細胞数)を増やすとさらなる面積が必要。

2.長い渦巻き状マルチモード光導波路構造

進む速度が異なる光波が多数存在できるマルチモード光導波路の性質を利用して現在の情報と過去の情報と混ぜ合わせるために長い(4cm程度)光導波路が必要とされる。渦巻き状に収容しても2mm ×2mm程度の面積が必要。

今回の試作では、構造2に比べて導波路幅を2倍広くし、さらには蛇行状の導波路構造を採用して長さを調整することにより、短い導波路長でゆっくりと進む光波(高次モード)を多数発生させ、さらには信号の高速化することで現在の情報と過去の情報が十分に混ざり合うように設計した。

今回の成果はCLEO2023(The Conference on Lasers and Electro-Optics)において採択され、2023年5月8日(現地時間)に発表した。

(詳細は、https://www.kddi-research.jp)