Science/Research 詳細

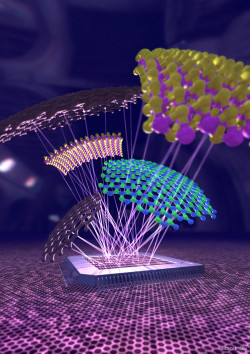

グラフェンと2D材料でシリコン技術強化

November, 12, 2019, Ahrensburg--ICFOの研究者によると、シリコン技術は、1960年だ後半から発展してきたが、回路の微小化は考えられる停滞に達したかに見える。トランジスタは一定のサイズに縮小し、それ以上に縮小できないからである。したがって、新しい材料でSi CMOSを補完する、将来のコンピューティング要件、アプリケーションの多様化要求を実現する差し迫った必要性がある。

現在、グラフェンと関連する2D材料が、原子極限で、デバイス性能において前例のない進歩の展望を示している。その驚くべき可能性は、Si技術の限界を克服する考えられるソリューションとなることが証明されている。ここでは、2D材料とシリコンチップの組合せが、現在の技術的限界を凌駕することが見込まれている。

Natureのリビュー記事では、ICFOの研究者を含む国際研究チームが協働して薄い原子厚の材料とシリコンペース技術との統合の機会、進捗、課題について詳細に、徹底的に見直している。研究チームは、2D材料が既存技術によって課された課題を克服する方法と理由を洞察し、デバイスコンポーネントの機能とパフォーマンスの両方を強化する方法について洞察している。これは、コンピュータおよび非コンピュータアプリケーション分野で、将来技術の機能を高めるためである。

非コンピュータアプリケーションでは、研究チームは、将来のカメラ、ローパワー光データ通信やガスおよびバイオセンサ向けにこれらの材料の考えられる組み込みをを見直している。特に、センサとフォトディテクタでは、グラフェンと2D材料(2DMs)が、可視光域に加えて、新たに赤外とテラヘルツ域で見ることができるようにする。これらは、例えば、自律走行車、空港のセキュリティ、拡張現実(AR)で役立つ。

コンピュータシステムでは、2DMsとSi技術を集積する際に、特にトランジスタ領域で、ドーピング、接触抵抗、誘電体/カプセル化なとの課題がどのように解決されるかを示している。2DMsは、メモリやデータストレージデバイスを根本的に改善する。これは、メタ-絶縁物-金属構造で新たな切替え機構によるものである。また、メモリアレイでは、漏洩電流を避けられる、あるいはグラフェンを超薄型銅バリア材料に接着して抵抗、散乱や自己発熱を減らすことでで、銅線ベース回路の性能利得をを押し上げることさえできる。

リビューは、2D材料のCMOS技術との統合を解決する課題と影響についてすべての関係事項を洞察している。それは、2D集積とCMOS技術のロードマップを示し、成長、移行、インタフェース、ドーピング、接触および設計の現在の段階を指摘し、研究環境から、両技術を統合する初のデバイスを製造するパイロットラインへ移行するという目標達成のために解決されるべき可能なプロセスを指摘している。

初の2D材料-CMOSロードマップは、今後数年で、初のパイロット製造が見えている。

(詳細は、https://www.icfo.eu)