Science/Research 詳細

産総研、半導体中のマイクロメートルスケールの電荷分布を可視化

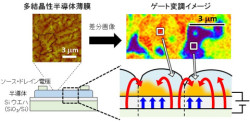

June, 26, 2018, つくば--産業技術総合研究所(産総研)と筑波大学の研究チームは、産総研が独自に開発した薄膜トランジスタ(TFT)の電荷を可視化するゲート変調イメージング技術の、空間解像度を810nmから430nmにするとともに、時間分解能を3µsから50nsに大幅に向上させた。この技術により、多結晶性半導体中の結晶粒界付近で電荷が不均一に分布する様子や、結晶粒界が電気伝導を阻害する様子を可視化できた。

ディスプレイやセンシングデバイスなどの情報入出力機器の大面積・軽量・フレキシブル化や、製造工程の簡略化・省エネルギー化に向けて、多結晶性半導体薄膜を用いたTFTの性能向上が課題となっている。多結晶性半導体の課題は、結晶粒界などに起因する不均質な構造が、性能低下の要因となることである。今回、TFT内に蓄積した電荷を可視化するゲート変調イメージング法の空間解像度と時間分解能を向上させ、多結晶性半導体の結晶粒界に起因するマイクロメートルスケールの不均一な電荷分布を可視化するとともに、結晶粒界付近の電気伝導の様子を50ナノ秒の時間分解能で捉えた。この成果は、多結晶性半導体内の電気伝導を可視化できる技術として、TFTの特性改善や高品質化に大きく貢献すると期待される。

研究チームの構成は、産総研フレキシブルエレクトロニクス研究センターフレキシブル材料基盤チーム堤潤也主任研究員、同研究センター長谷川達生総括研究主幹、松岡悟志産総研テクニカルスタッフ(兼)筑波大学数理物質科学研究科博士課程学生。

この成果の詳細はJournal of Applied Physics, vol.123, 135301 (2018) とPhysical Review Applied, vol.9, 024025 (2018) www.aist.go.jp次いで掲載された。

(詳細は、www.aist.go.jp)