Science/Research 詳細

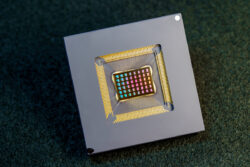

エッジAIに新しいニューロモルフィックチップ

September, 15, 2022, San Diego--NeuRRAMチップは、初のコンピュータ・イン・メモリチップ。他のプラットフェームの消費エネルギーのほんの一部で、同等の精度を維持しながら、広範なAIアプリケーションを実証する。

国際研究チームは、メモリで直接計算を行い、広範なAIアプリケーションを実行するチップを設計、作製した。全て、汎用目的のAIコンピューティングの計算プラットフォームが消費するエネルギーのほんの一部で実行する。

NeuRRAMニューロモルフィックチップによりAIは、クラウドから切り離されて、動作する広範なエッジデバイスに一歩近づく。デバイスは、高度な認知タスクをどこでも、いつでも実行できる、集中サーバへのネットワーク接続に依存する必要はない。アプリケーションは、世界の隅々に、われわれの生活のあらゆる側面にある、スマートウオッチ、からVRヘッドセット、スマートイヤホン、工場のスマートセンサ、宇宙探査のローバまで。

NeuRRAMチップは、最先端の「コンピュータ・イン・メモリ」チップの2倍のエネルギー効率、メモリで計算を実行する革新的なクラスのハイブリッドチップであるだけでなく、従来のデジタルチップ同様の精度で結果を生み出す。従来のAIは、遙かに大きく、一般にクラウドで動作する大規模データサーバの利用に制約されている。

加えて、NeuRRAMチップは、汎用性が高く、多くの多様なニューラルネットワークモデルやアーキテクチャをサポートする。結果、そのチップは、多くの多様なアプリケーションに利用できる。画像認識や再構築、音声認識など。

「一般的な見解では、コンピュータ・イン・メモリの効率が高くなれば、汎用性が犠牲になる。しかし、われわれのNeuRRAMチップは、汎用性を犠牲にすることなく効率を獲得する」と論文の著者、Weier Wanは説明している。

UC San Diegoでバイオエンジニアを共同リーダーとするチームは、研究成果をNatureに発表した。

現在、AIコンピューティングは、パワーハングリーであり、計算コストが高い。エッジデバイスのほとんどのAIアプリケーションは、データをデバイスからクラウドに移動する必要がある。そこでAIがそれを処理し、分析する。次に、結果がデバイスに戻ってくる。それこそが、ほとんどのエッジデバイスがバッテリパワーで動作し、結果的にコンピューティング専用にできる電力量が限られる理由である。

エッジでAI推論に必要な電力消費を減らすことでこのNeuRRAMチップは、よりロバスト、スマートで利用しやすいエッジデバイス、よりスマートな製造になる。また、データプライバシーの改善にもなる。デバイスからクラウドへのデータの移転は、セキュリティリスク増となるからである。

AIチップでは、メモリからコンピューティングユニットへのデータの移動が、一つの主要なボトルネックである。

「1日2時間労働のために8時間通勤するようなものだ」(Wan)。

このデータ移転問題を解決するために研究チームは、抵抗型ランダムアクセスメモリ、一種の不揮発性メモリとして知られているものを利用した。これにより、計算が、別のコンピューティングユニットではなく、メモリ内で直接行われる。ニューロモルフィックコンピューティングにシナプスアレイとして使われているRRAMや他の新しいメモリ技術は、Philip Wongのラボで開発された。同氏は、スタンフォードでWanのアドバイザであり、この研究の主要貢献者である。RRAMチップによるコンピュテーションは必ずしも新しくないが、一般にそれは、チップで行われる計算精度低下、チップのアーキテクチャにおける柔軟性欠如となる。

「メモリ内の計算は、30年以上前に導入されたので、ニューロモルフィックエンジニアリングでは一般的な方法である。NeuRRAMで新しいのは、極度の効率が、様々なAIアプリケーションの大きな柔軟性と両立することである。標準的な汎用計算プラットフォームで正確さはほとんど失われない」(Cauwenbergh)。

ハードウエアとソフトウエアの抽象化層で、チップの設計から、様々なAIタスクを走らせるその構成まで、マルチレベルの「共同最適化」を持つ成果のカギは、注意深く構築された方法論である。加えて、チームは、メモリデバイスの物理学から回路およびネットワークアーキテクチャまでの範囲の様々な制約を忘れずに考慮した。

「このチップによりわれわれは、デバイスや回路からアルゴリズムまでのスタックでこれらの問題に対処するプラットフォームを手に入れた」と、ノートルダム大学、コンピュータ科学&エンジニアリング准教授、Siddharth Joshiは話している。同氏は、UC DavisのCauwenberghs研究室で、Ph.D学生、ポスドク研究者として同プロジェクトへの取組を始めた。

チップのパフォーマンス

研究チームは、エネルギー遅延積(EDP)として知られている評価基準でチップのエネルギー効率を計測した。EDPは、全オペレーションで消費されるエネルギー量とオペレーション完了にかかる時間の両方を統合している。この評価基準によりNeuRRAMチップは、最先端のチップと比べて1.6~2.3倍低いEDP(低いほど良い)、7~13倍高い計算密度を達成している。

研究チームは、、そのチップで様々なAIタスクを実行した。手書き数字の読取りでは99%の正確さを達成。画像分類タスクは85.7%、Googleスピーチコマンド認識タスクでは84.7%を達成した。加えて、チップは、画像回復タスクでは、画像再建エラーを70%減らした。これらの結果は、同じビット精度で計算を行う既存チップに匹敵するがエネルギー消費は激減である。

研究者の指摘によると、論文の重要貢献の1つは、掲載された全ての結果がハードウエアで直接得られることである。メモリ内コンピュートチップの多くの以前の研究では、AIベンチマーク結果は、ソフトウエアシミュレーションによって部分的に得られることが多かった。

新たなステップは、アーキテクチャや回路の改善、設計を改善してより進んだ技術ノードにすることを含む。研究チームは、スパイキングニューラルネットワーク(SNN)など、他のアプリケーションへの取組も計画している。

「われわれは、デバイスレベルでもっとうまくできる、回路設計を改善し、付加機能を実装して、われわれの動的NeuRRAMプラットフォームで多様なアプリケーションを処理する」とピッツバーグ大学准教授、Rajkumar Kubendranは、コメントしている。同氏は、UC San Diegoの研究グループのPh.D学生としてプロジェクトに参加した。

加えて、Wanは、メモリ内コンピュート技術の製品化に取り組むスタートアップの設立メンバーである。

チップのアーキテクチャ

NeuRRAMのエネルギー効率のカギは、メモリの出力センシングの革新的方法である。従来のアプローチは、インプットとして電圧を使い、結果としての電流を計測する。しかし、これは、より複雑でパワーハングリーな回路を必要とする。NeuRRAMでは、チームは、電圧を感知し、エネルギー効率の良い方法でアナログからデジタルへの変換を行うニューロン回路を設計した。この電圧モードセンシングは、1回の計算サイクルでRRAMアレイの全ての行と全ての列を活性化するので、並列性向上となる。

NeuRRAMアーキテクチャでは、CMOSニューロン回路は、RRAMウエイトにより物理的インタリーブされている。それは、CMOS回路が一般にRRAMウエイトの周囲にある従来の設計とは異なる。RRAMアレイとニューロンの接続は、ニューロンのインプットあるいはアウトプットのいずれかとして働くように構成可能である。これにより、様々なデータフロー方向におけるニューラルネットワーク推論が、可能になる。エリアのオーバーヘッド、パワー消費は発生しない。これは、今度は、アーキテクチャの再構成を容易にする。

AI計算の正確さが様々なネットワークアーキテクチャで確実に維持されるために研究チームは、一連のハードウエアアルゴリズム共同最適化技術を開発した。その技術は、畳み込みニューラルネットワーク(CNN)、長い短期記憶、制限ボルツマンマシーンを含む様々なニューラルネットワークで検証された。

ニューロモルフィックAIチップとしてNeuRRAMは、48のニューロシナプスコアで並列分散処理を行う。高い汎用性と高効率の同時達成のためにNeuRRAMは、データ並列性をサポートしている。ニューラルネットワークモデルのレイヤをマルチデータで並列推論するためのマルチコアにマッピングすることによって行う。また、NeuRRAMは、様々なモデルレイヤを多様なコアにマッピングし、パイプライン形式で実行することによりモデル並列性を提供する。

(詳細は、https://ucsdnews.ucsd.edu/pressrelease/Nature_bioengineering_2022)