Science/Research 詳細

標準CMOSプロセスで200mmウエハにIII-Vシリコンレーザ集積

December, 12, 2017, Grenoble--CEA Techの研究所、Letiは、標準CMOSプロセスフローを使って、ハイブリッドIII-Vシリコンレーザを200mmウエハに集積した。このブレイクスルーは、100mmウエハとバルクIII-V技術ベースのプロセス、貴金属との接触およびリフトオフベースのパタニングを必要とする技術からの移行法を示している。

Leti主導のIRT Nanoelecプログラムで実施されたプロジェクトは、ハイブリッドデバイスのパフォーマンスが、現在の100mmウエハのプロセスで製造されたレファランスデバイスに匹敵することを実証した。

研究成果は、IEDM 2017で「200mm完全CMOS適合シリコンフォトニクスプラットフォームハイブリッドIII-V/Si DFBレーザ集積」として発表された。

シリコンフォトニクスに適合するCMOSは、製造コストを削減し、成熟した大規模ファシリティへのアクセスを提供する。これはCMOS駆動回路に適合するパッケージングを可能にする。

「シリコンフォトニック技術は、成熟が進んでいるが、これらのプラットフォームの主要な限界は、集積光源が欠如していることである」と論文の共著者、Bertrand Szelagは指摘している。「このプロジェクトは、モジュラーアプローチで、成熟したシリコンフォトニックプラットフォームにレーザを集積できることを示している。プロセス全体が、従来のプロセスと材料を使い標準製造ラインで実施できること、またすべてのフォトニックビルディングブロックを大規模集積できることを実証した」。

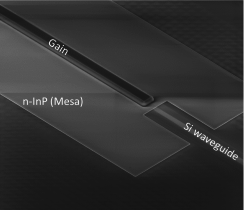

この集積では、ハイブリッドレーザ用には厚い、一般に500nm厚のシリコン膜、ベースラインのシリコンフォトニックプラットフォームにはもっと薄い、一般に300nmのシリコン膜を必要とした。これは、ダマシン(damascene)プロセスにより200nmのアモルファスシリコンを加えることでシリコンを局所的に厚くする必要があった。これによって、III-Vシリコンのボンディングに都合のよい平坦面が残る。レーザは、基準プロセス性能に妥協のないモジュラーアプローチで成熟したシリコンフォトニックプラットフォームに集積可能である。

このアプローチの新しさには、金のような貴金属を含まない革新的なレーザ電気接点の利用が含まれる。CMOSトランジスタ技術と同様の集積技術でニッケルベースのメタライズ使用した、ここではタングステンプラグがデバイスをルーティング金属線に接続する。

次のステップとしては、レーザとアクティブシリコン-フォトニックデバイス、たとえば変調器やフォトダイオードの集積がある。最終的に、III-Vダイボンディングは、シリコンウエハ全体でレーザを処理するために、III-Vウエハボンディングを置き換えることになる。

(詳細は、www.leti-cea.com)