ニュース 詳細

T型フィルタ、伝送線路とEMC

EMCの犠牲を強いることのないシグナル・インテグリティを経験したことはあるだろうか?答がイエスなら、この悪夢のような経験をせずに済んでラッキーといえる。

I. 状況

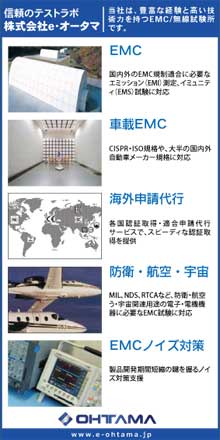

I2Sバスマスタークロックドライバを12.288 MHzにセットし、3.3 Vで動作させる。出力駆動力は50 Ωで、立ち上がり時間2 ns、立ち下がり時間は2 nsである。ドライバは「マスター基板」上に設置され、バスラインは長さ4インチのトレースを通って基板用コネクタに達する。シグナルはこのコネクタから長さ4インチのフレックスケーブルを通って別の「スレーブ基板」を経由する。この「スレーブ基板」上でバスラインはあと6.5インチ進んで目的地のレシーバに到達する。驚くことに、図1のとおり、このレイアウトのシグナル・インテグリティは、問題ないように見える。

だが、期待できそうな絵のウラに隠れているのがEMC性能である。図2に、このクロックの放射エミッション(RE)を示す。

図2では135 MHz、160 MHz、184 MHzでスパイクが見られる。つまりフレックスケーブルを通して放射しているマスタークロックの11番目、13番目、15番目の高調波がエミッション限度値を超過していた。EMC設計エンジニアは、この問題に対処するためT型フィルタ(ムラタ製NFL18ST506H1A3D)を「マスター基板」上のフレックスケーブルコネクタの入力部に設置した。このフィルタのカットオフ周波数は50 MHzである。図3に示すとおり、フィルタの取付は放射エミッションに劇的な効果をもたらした。

図3の見た目は極めて良好である。5 dBのマージンはEMCの世界で贅沢といってよい。しかし、マージン5 dBの至福は長くは続かず、マスタークロックラインをシグナル・インテグリティ(SI)で再分析すると図4の結果となってしまった。

T型フィルタを伝送線路に追加することで静電容量110 pFがグランドに追加され、結果的に位相シフトによる反射が起きる。この反射が原因でVOLマージンは失われ、エッジ検出の失敗が懸念されることになった。

II. フィルタを使わないソリューションの考慮

注意:手順および要求の制約により、設計チームがレイアウト変更に関する提案を全て拒んだので、他のソリューションを考える必要が出てきた。

●駆動力を削減する

立ち上がリ/立ち下がり時間を増やすと反射を隠すことができるが、常時というわけではない。このソリューションは、伝送線路の長さが14インチでない場合に有効である。駆動力の削減はEMCには非常によく働くが、結果的に伝送線路は駆動できなくなる。

●線間電圧を削減する

マスタークロックは3.3 Vで動作する一方、I2Sバスは1.8 Vで何の問題もなく動作可能である。ラッキーなことに、ゼロオームの抵抗を装着するパッドのあるPCB上にレベルシフタを取り付けるプレースホルダ(事前に確保している場所)があった。レベルシフタの取り付けによって線間電圧は3.3 Vから1.8 Vに下がり、SIでは図1同様の、放射エミッション性能では図3に似た結果となった。

III. この種の問題を避けるために

●伝送線路を短くする

I2Sドライバとレシーバの間の伝送線路はなるべく短い方がよい。「マスター基板」から「スレーブ基板」へ流れるバスの理想的な状況は、基板の入出力コネクタの近くにドライバとレシーバを置くことである。検討例では、「スレーブ基板」のトレース長が非常に短い場合、T型フィルタを設置してもSI問題は起きなかった。

●適切なインピーダンス

設計上の制約のために伝送線路の長さを抑える場合、伝送元と伝送線路の負荷のミスマッチが起こらないよう留意することが重要である。直列のマッチングあるいは並列のマッチングというスキームを考慮してもよい(Clayton R. Paul氏が2006年に書いた「Introduction to Electromagnetic Compatibility」第4章を参照)

●ビアを避ける

伝送線路がビア経由でボードレイヤにクロスする場合の事例を見てきた。伝送線路の断面寸法が変化すると線の特性インピーダンスが変化し、その不連続点で反射が起きる。ビア経由の信号は不連続性に直面することになる。

●SIの割当て

伝送線路のSI割当てを決定することは重要である。これは設計のレイアウト段階で可能である。Cadence/Allegro/Spice などのツールを使って、伝送線路に静電容量、インダクタンス、DCR(DirectCurrent Resitance:直流抵抗)を追加すれば、マージン/帯域幅エラーの起きる周波数帯域は計算できる。これを実施すると、例えば伝送線路にどれぐらいの静電容量を追加し、かつ良好なSI を保つことができるかということがわかる。

IV. 要約

伝送線路のレイアウトは、SIの設計をしっかり実践した後に適切に実行すべきである。良好なSIは、SIを歪曲することなくT型フィルタ(または他の手段やフィルタリング)を設置するなどのEMC対応(必要な場合)を実施するマージン/帯域を提供する。最後になるが、部品を基板に組み上げる前にEMCエンジニアにレビューしてもらうのが良い考えであるのは言うまでもない。

図1.I2S バスマスタークロック

図2.I2S バスマスタークロックの放射エミッション

図3.T 型フィルタを取り付けた場合のI2S バスマスタークロックの放射エミッション

図4.T 型フィルタを取り付けた場合のマスタークロックのSI