ニュース 詳細

デジタルICに対するESDの影響

シールドされていない家電や市販の機器で非常によく目にする問題の1つは、静電放電(ESD)試験中などのイミュニティ試験中にCPUがリセットすることである。これに未対応のままでは、現場での故障や、ひいては顧客の満足度にも関わってくる。

通常、対応方法は非常にシンプルであり、ICメーカーはもちろん解決法を公表しているのだが、ふつうはデータシートのどこかに埋もれてしまっている。解決策とは、R-Cローパスフィルタである。

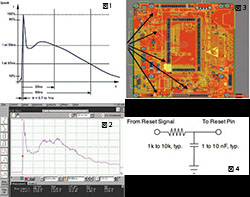

図1は、(IEC 61000-4-2 規格からの)ESD波形を単純化して表したものである。ESD電流パルスには一般的に1ナノ秒より大幅に短い立ち上がり時間がある。

1.5 GHz帯域オシロスコープだけを使って測定したので、平均の立ち上がり時間は図2にあるとおり575ピコ秒であった。別の非常に速いオシロスコープを使用した際は35ピコ秒と速い立ち上がり時間を測定したことがあるので、これは明らかに帯域幅の制約によるものである。

私の顧客の1人は、ESDによって組込プロセッサのCPUリセットを妨害されるという厄介な問題を抱えていた。使用している回路は一般的なもので、多くのI/Oコネクタがエッジの周りに配置されていた。USBケーブルを接続しただけでプロセッサがリセットしてしまう。人が近くを歩くことで発生するESDでさえ休止を引き起こした。

私はPCの回路レイアウトを調べ、CPUリセット信号トレースが全てのコネクタにどのようにつながり、回路を数センチにわたって交差するか矢印で図示した(図3)。もちろん、このように長いリセットトレースは非常に優秀な受信アンテナとして機能し、ESDによる電磁界に容易に結合する。

前述したように、解決策はシンプルなR-C ローパスフィルタである。値は重要ではなく、通常、抵抗器1 k~10 kオーム、コンデンサ1~10 nFでよい。

IC に対するESDの影響に関する試験やトラブルシューティングの詳細は、2017年4月25日~27日実施の「ESDと効率的な電子機器設計を探り、問題を解決する」という無料のウェブセミナーも参考にしていただきたい。ゲストスピーカーはLanger EMVTechnik社のSven König氏。(セミナーURL:http://emc.live/)

このウェブセミナーでは電子機器設計におけるIC の動作、特にESDの特性と、そのICへの影響が機器にどう影響するかをテーマにしている。ESD問題を特定するには、設計段階でIC レベルの妨害を再現する特別な試験セットアップの使用が必要になる。これによりエンジニアは開発に要する時間と労力を節約することができる。ESD問題のいくつかは電子・IC レベル両方の具体例によって説明・補完できると思われる。

図1.IEC 61000-4-2規格に準じた理想的なESDパルス

図2.ESD電流パルスの測定値。546ピコ秒から600ピコ秒の立ち上がり時間を示している。

図3.全てのCPUリセットトレースを示す矢印

図4.シンプルなR-Cローパスフィルタを全てのCPUリセットピン上に使用し、ESDやEFTなどの過渡電流を除去する。