ニュース 詳細

ESD抑制ダイオード配置の重要性

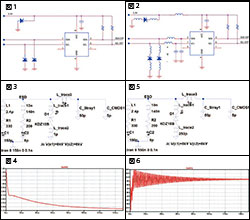

過渡電圧抑制(TVS)ダイオードを用いた敏感な電子機器のESD保護は、業界を通じて一般的な回路技術になってきている。人間が触れることのできる回路(USB、HDMIなど)にある信号線では、何らかのICに入力されている敏感な信号線全てにおいてESD保護が必要である。ダイオードが保護しているICに関連する回路基板のESD保護ダイオードの配置は、非常に重要な役割を果たしている。ESDのような過渡的な現象での信号のPCBトレースの動作を理解することは重要である。例として、TVSダイオードを持つI2Cバス機能拡張の回路図を図1に示す。

ESDの過渡現象を表す現実的な等価回路を図2に示す。

PCBトレースには、長さに応じて、関連するインダクタンスがある。SDA信号トレース(図1参照)を考えてみよう。下記のポイントに接続するトレースの長さは非常に重要である。

• ノードAからダイオードの陰極に至るトレースの長さ

• ダイオードの陽極からグランド接続に至るトレースの長さ

• ノードAからICの入力ピンに至るトレースの長さ

言い換えると、ESD保護ダイオードは保護しているピンのできるだけ近くに配置すべきであり、基準面への接続は、陽極ピンにできるだけ近くする必要がある。そうでなければ、上記のどこのポイント間でもトレースのインダクタンスが十分に大きくなり、IC の入力容量とトレースの浮遊容量が原因でタンク回路が生成されることもある。タンク回路は、ICの入力電圧能力を超えうる電圧で振動し、ICに重大な被害を与えかねない。

このシナリオはLTSpiceをモデルにした。図3はLTSpiceに生成された回路図を示しているが、図には2つのパーツがある。1つ目はIEC 61000-4-2の試験方法に基づくESDの人体モデルである。2つ目は、トレースSDAのための図2の説明である。図3の説明は、上述のポイント全てで非常に短いトレースを保って適切に配置された(10 Vのクランプ)ダイオード用で、それゆえ結果的にトレースインダクタンスは非常に小さい。図4は、CMOSに基づく入力(コンデンサにより表される)での電圧を示す。

ESD保護ダイオードが可能な限り短いトレースを保って適切に配置された場合、ESDパルスはダイオードによって安全なレベルまで低減される。このダイオードおよび配置は、ICをESDから十分に保護している。

一方、図5は適切に配置されなかった(10 Vのクランプ)ダイオードの回路である。ノード Aから図2のダイオードの陰極へのトレースは、長さ約1インチ(25.4 mm)で、およそ1 nHと概算できた。陽極からグランドへのトレースは同じく約0.03インチ(0.762 mm)、およそ250 pH。

図6は、(コンデンサによる)入力に基づくCMOSでの電圧を示している。

図6が示しているのは、長いトレースがダイオードの陰極から信号線の結節点へ、およびダイオードの陽極からグランドへ与える明らかな影響である。トレースインダクタンス、配線の浮遊容量、ICの入力容量により決まる周波数で、ピーク電圧が21 V の減衰振動が観測された。

【結論】

I/O線におけるESDが原因の振動を最小に抑え、ICの損傷を避けるには、以下のことに注意すべきである。

• クランプ(TVS)ダイオードは、できるだけICピンの近くに配置する。• ダイオードの陰極へつながるトレースは、できる限り短くする。• ダイオードの陽極からのグランドリターンへつながるトレースは、できる限り短くする。

図1.TVS保護機器の一般的な回路図

図2.トレースインダクタンスと寄生容量を示す一般的な等価回路

図3.適切に配置されたダイオードのLTSpice ES回路モデル

図4.適切に配置されたダイオードのCMOSベースの入力における電圧

図5.適切に配置されていないダイオードのLTSpice ESD回路モデル

図6.適切に配置されていないダイオードの入力に基づいたCMOSでの電圧