# • feature CMOS センサ

## CMOSとCCD統合により NIR TOFオンチップイメージャを実現

ビート・デ・コイ、スティーブン・フリードマン

全電荷ハンドリング容量と低雑音動作を維持しながら、モノリシック CCD システム・オン・チップ技術は、今では CMOS 環境に組み込まれている。そこでは、背面照射と厚くなったディテクタボリュームによって、感度はけた違いに向上している。

過去数十年、イメージングの世界ではCCD(電荷結合素子)とCMOS(金属酸化膜半導体)技術との比較で多くの文献が著されている。どちらかのアプローチの優位性についての激しい議論や熾烈な論争さえも当たり前になっている。

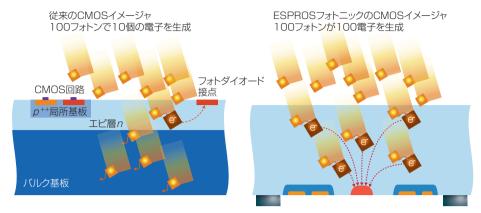

こうした対立に応えてESPROSフォトニクス社は、厚い基板を持つ背面照射イメージャを開発した。このイメージャは、近赤外(NIR)光パフォーマンスを改善しながら、CCDとCMOS技術を統合している。この真のシステム・オン・チップ(SoC)飛行時間(TOF)イメージャにより、改善された時間遅延イメージング(FLIM)という成果が可能になる(外観写真参照)。

#### 従来の問題点

市販のCMOSイメージセンサ (CIS) モジュールをみても、標準CMOSプロセスはNIR 照射の検出にあまり適していないと言える。これは、一部にはピンド・フォトダイオード (PPD)の感受性領域の厚さが数 $\mu$ m しかないためである。これは光の吸収長 (シリコンでは850nmの光で約13 $\mu$ m: 図1)よりもはるかに少ない。

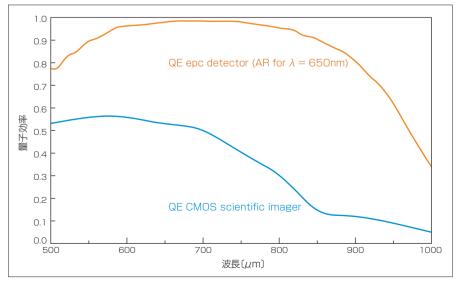

基板材料で光の吸収長、空乏域の厚さ(さらに、下の追加拡散領域)、表面の

反射特性が組み合わさり、所定の波長 でイメージャの量子効率 (QE)が規定 される。

標準フォトディテクタでこれらのパラメータの最適化は、CMOSもしくは CCD製造工程による境界条件の制限を受ける。例えば、空乏域は商用プロセスで利用できるエピタキシャルの厚さに制限され、一方光反射特性はバックエンド(BEOL)スタックに規定される。つまり、干渉縞により、BEOLスタックは波長に対してQEの支配的な変動要因となる。

しかし、CMOSとCCD特性を統合する同社の新しい混合プロセスは、これらの制限に対処している。特に、適切な基板材料の選択が、厚さ50μmの完全空乏ディテクタに寄与する。この結果、波長850nmで>80% QEと波

長950nmで>50%を維持しながら、NIR領域における優れたQEが得られる(図2)。

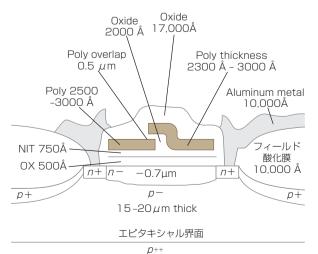

#### CCD-CMOS統合

標準CMOSプロセスで効率のよい CCDを実現するには、デュアルポリシ リコンアプローチで良好な電荷移動効 率(CTE)を達成する必要がある。CCD ゲートは、1つのポリ層から他のポリ 層にオーバーラップしており、非常に 薄い酸化被膜で分離されているだけで ある。薄く、よくコントロールされた ポリ層が高CTEの決め手になる(図3)。

しかし0.25μm以下のサイズを使うことで、デュアルポリはもはや可能ではなくなる。180nm以下で始まるプロセスノードがBEOLで化学機械研磨(CMP)を使用するからである。CMPは、層堆積と構造化で確実にフラットな表面を必要とする。したがって、2番目のポリシリコン層はもはや可能ではなくなる。良好なCTEの決め手は、2つのゲート間の非常に狭いポリギャップで

図1 従来のCMOSイメージは、100の入 射フォトンあたり10個の電子を生成する。 しかし、ESPROSのハイブリッドCCD-CMOSイメージャは、ほぼ1対1の比であり、 100の入射フォトンに対して最大90個の電 子が生成される。

ある。そのようなナローギャップは、45nm (それ以下)のプロセスを使うことで簡単に達成できる。しかし、そのような技術ノードの開発および装置コストは法外に高価であるので、CMOSへのCCD導入の候補としては、それは除外される。ESPROSの技術は、新設計の製造工程によってこのジレンマに取り組む。この新しい製造プロセスにより、100nm以下のポリゲートが、標準の180nmプロセス環境でも可能になる。

50μm完全空乏シリコンディテクタボリュームは、この混合プロセスによるイメージャの感度で大きな要因の1つをなす。その深さが、標準的なCMOSプロセスで薄いエピタキシャル層を透過するだけのフォトンをバルク基板で吸収できるようにするからである。ここでは、フォトンは無駄なエネルギーを熱として生成する。もちろん、そのように厚いディテクタボリュームでは、電子-ホールペアを分離してCCDゲート下の電子を収集するには、十分に高い電界が必要になる。

さらに、標準的なCMOSフロントサイドイメージャでは、トランジスタがチップ前面の光路に置かれている。これらのトランジスタは、入射フォトンによる活性化から保護されなければならない。しかし、これらのトランジスタをブロックする不要な効果は、光

の収集に利用する表面積を大幅に減らすことにもなる。それに対して、この新しい混合プロセス環境では、トランジスタが存在しないイメージャの背面を使って光を収集する。この背面照射で達成される100%のフィルファクタと50μm厚ディテクタボリュームQEゲインとを結びつけることにより、標準的なCMOSに対してけた違いの感度向上が可能となった。

イメージャは背面照射 (BSI)であるので、しっかりと調整された反射防止 (AR)膜を適用することで、所望の波長 範囲でディテクタの反射を低減できる。また、背面の入光ウインドウは破壊的

な酸化物スタックがない完全フラット であるので、標準的なウエハレベルプ ロセスを用いて屈折率フィルタを堆積 することができる。

この製法により、ディテクタの背面 に狭帯域のフィルタバンクをつけるこ とが可能になり、様々なモバイルアプ リケーション向けの超小型分光計が実 現可能になる。この新しいアプローチ は、入射ウインドウの金属スタックを 削除して、改善された光学デザイン向 けに大きな入射角とすることができる ので好都合でもある。

向上したQEは、そのままレシーバ の感度となる。アプリケーションの視

図2 の標準CMOSまたはCCD設計と比べて、ハイブリッドCCD-CMOSアーキテクチュアは、近赤外領域のイメージャで、量子効率の大幅改善となっている。

点から、特に飛行時間(TOF)アプリケーションでは、改善されたQEを活用して照射パワーを著しく低下することができる。また、一定の信号強度(照射パワー)を得るために照射時間を減らすことができ、カメラシステムは動くターゲットによるブラー効果に左右されなくなり、太陽光に対しても耐性が高くなる。

現場に存在する太陽光は、直流(DC)、非変調背景雑音となり、これは検出すべき信号よりも何ケタも大きい。しかし、これらCCD-CMOSピクセルの特別な特性により、DCバックグラウンドの効果はほぼ完全に除去される。この点は、様々な実世界環境でTOFを使って正確に距離を測定するには非常に重要である。

裏面コンタクトは、プロセス特有の 特徴であり、全ての物理コンタクトは チップの前面に残っている。

#### 両者の長所

QEを最適化するために展開されたこのような方法は、CCDとCMOSの特性統合を成功させるのための厳しい前提条件というわけではないが、個々の技術の欠点の軽減を容易にする。例えば、CMOSはグローバルシャッタ方式を実現するには各ピクセルにトランジスタを追加する必要があるが、これは通常、フィルタバンクにおける損失の原因となり、応答性に悪い影響を及ぼす。しかしこの新しいハイブリッドプロセスでは、シャッタリングは電荷ドメインで完全に実行され、ナノ秒となるように制御することができる。

また、専用のフレームバッファにおけるフレームストア機能を持つ繰り返しシャッタリングもわれわれの設計により実現されている。 高電圧トランジスタ、電気的に消去できるプログラマブ

ル読み出し専用メモリ(EEPROM)ブロックを含め、完全CMOSアナログ設計の特徴は、フィルファクタで妥協することのないピクセルアーキテクチュアに残っている。実際、この背面照射(BSI)ベースのハイブリッド光ディテクタは100%のフィルファクタを提供でき、実質的にピクセルのトランジスタの数に依存しない。

われわれのハイブリッドディテクタのCMOSベースラインプロセスは、臨界ノード幅150nm、1ポリマ6金属(1P6M)プロセスをベースにしている。このプロセスノードにより、高密度CMOS設計機能が可能になる。しかし、もっと重要な点は、小さな構造により、 $100\mu$ V/eまでの極めて高い変換利得のソースフォロアが可能になることである。これら微光対応低雑音イメージャは、FLIMやTDIイメージングに適している。

ノイズ性能は、正確なTOF計測能力に大きく影響する。混合プロセス環境に可能な範囲でノイズ性能に取り組むと、CCDピクセルデザインには、そのノイズ的優位性がすべて適用できる。さらに、ピクセル内のソースフォロアは、BSIによるサイズ制限を受けず、CMOS読み出しや増幅段は最高のパフォーマンスを出せるところで展開

できる(高利得増幅器など)。

さらに結果として、ダイナミックレンジは大きな電荷量を蓄積し取り扱う能力から利益を得る。加えて、ピクセルデザインにおける自由度は、専用の高ダイナミックレンジアーキテクチュア実現をサポートする。その上、他の全ての要素が同じなら、ノイズの振る舞いを改善するように、より高電荷を供給することで、前述のQE優位性が極めて重要な脇役を演ずることになる。

特にTOFアプリケーションでは、スピードが基本的要件である。イメージング速度は、効率的なフォトン変換とそれに続く電荷収集メカニズムによって決まる。このメカニズムを制限するのが拡散であり、またそのメカニズムは印加された電圧のデプリーションレベルに関連したドリフト速度の制約を受ける。

CCD構造を実現することで素早い電荷ハンドリングが可能になり、蛍光 分光計用の時間ゲートセンサのような新しい機能が実現する、あるいはTOFシステムにおける位相差の検出が可能になる。TOFイメージャでは、受信信号に取り組むために必要となる時間分解能はサブナノ秒(50ps以下)である。同時に、変調光よりも数ケタ高い環境

図3 デュアルポリ CCD。電荷移動は、左(直線)と右(オーバーラップ)のポリゲートで起こる。2つのゲートがオーバーラップしているので、Nウエルにおける仮想バケットの横方向分離は実質的にゼロである(情報源:ジェイムス R.ジェインシック、Scientific Charge-Coupled Devices, SPIE Press)。

### • feature cmostat

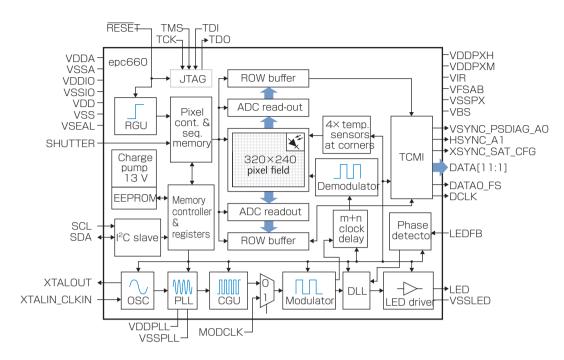

図4 ESPROS混合プロセスイメージャは、最適NIRセンサに必要とされる全てのサブシステムを含んでいる。そのセンサは、CCDとCMOS技術の最良部分と高い量子効率を統合している。

光が存在する。当社のハイブリッド CCD-CMOSアプローチで実現したような強力な荷電分離と荷電ハンドリン グエンジンがなければ、深さ分解能は 実用価値を遙かに超えるか、あるいは 環境光信号によって完全に覆い隠され るか、あるいはその両方となる。

しかしまた、さらに一歩進んでイメージングシステムのスピードに着目すると、CMOS技術は超高速の最先端のSoCソリューション設計では大きな優位性がある。

#### オンチップイメージング

これまで、全てのTOFデザインは、 背景雑音、移動物体、ターゲットの反 射性の大きな変動など、一般的な環境 条件に対して堅牢さを欠いている。加 えて、これらのセンサデバイスは、複雑 で高価な周辺コンポーネント、FPGA、 高速ADC(アナログ・デジタルコンバー タ)、どちらかというと大きめの電圧 制御部などを必要としている。最後に、 サイズ、消費電力、市販カメラのコス トが今でも、大量商用利用を妨げる範 囲にある。

その代案として、ハイブリッドCCD-CMOS TOFイメージャは、これらの問題の多くを解決する。イメージャの中でも、遠隔モニタリング用のTOFシステムを作製するために、混合プロセス環境を使用した。このようなシステムは、照明や背景光条件で非常に大きな差がある工業規模のアプリケーションの影響を受けやすい。

64フレーム/秒速パラメータで、TOF SoC イメージャは全ての必要なサブシステムを含んでいる。これに含まれるのは、ピクセルアレイ、アナログドライバと電圧レギュレータ、平行性が高いADC、デジタルステートマシーンとタイミング生成、大電流LEDドライバ、デジタル信号処理、設定パラメータを格納するための不揮発性メモリなどだ(図4)。

そのSoCの主要素は、320×240ピクセルのQVGAである。これは、復調

信号特性にしたがい、2つの異なる読み出しノードに信号電荷を移動させることによって、各ピクセルに必要な復調を個別に行うことができる。したがって、各ピクセルは2つのアナログ読み出しチャネルを持ち、それらを解析して放射光パルスの位相との関連で位相差を決める。

ピクセル読み出しは、TOFアプリケーションでは、-4~+4の符号付入力範囲の12ビットADCで構成される典型的な信号チェーンを使用する。2つのソースフォロア出力差がサンプリングされ、正または負になる。

CCDとCMOSプロセス技術の統合により、1つの特定技術を考える際にこれまで存在したすべての既知のトレードオフが、今ではなくなっている。言うまでもなく、NIR範囲ではパフォーマンスが向上した光学シリコンディテクタが可能になっている。

#### 著者紹介

ビート・デ・コイは、スイス ESPROS フォトニクス社の CEO、スティーブン・フリードマンは米 ESPROS フォトニクス社のマネージングダイレクター。

e-mail: steven.freedman@espros.com URL: www.espros-photonics.com