Science/Research 詳細

電子/フォトニックチップサンドイッチでコンピュータとデータ転送効率向上

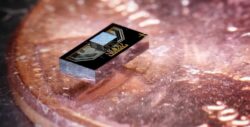

December, 13, 2022, West Lafyette--Caltechとサウサンプトン大学のエンジニアは共同で、フォトニックチップを集積した電子チップを設計した。作製された最終の密着製品は、超高速で情報を伝送し、発熱は最小限である。

2つのチップサンドイッチは、ラップトップには載りそうにないが、その新設計は、大容量のデータ通信を扱うデータセンタの未来に影響を及ぼす。

Caltech院生、Arian Hashemi Talkhoonchehは、「米国には2700以上のデータセンタがあり、世界では8000を超える。サーバタワーが相互にスタックされていて、秒ごとに数千テラバイトのデータの入出力を管理している」と話している。同氏は、 IEEE Journal of Solid-State Circuitsに発表された2-チップイノベーション論文の主筆。

ラップトップを使用していると熱くなるように、われわれ全てが接続しているデータセンタのサーバタワーも稼働により熱くなる、しかし、その規模は遙かに大きい。データセンタの中には、ファシリティ全体の冷却を容易にするように水中に構築されているものもある。データセンタの効率が向上すればするほど、発熱もますます少なくなり、最終的には、扱える情報量もますます多くなる。

データ処理は電子回路で行い、他方でデータ転送は、フォトニクスを利用して行うのが最も効率的である。各ドメインで超高速を達成することは、非常に挑戦的であるが、両者の間のインタフェースの設計は、さらに難しい。

「データセンタだけでなく、HPCsでも、異なるチップ間のデータ通信速度向上に継続的な要求がある。チップのコンピューティングパワーが拡大するにつれて、特に厳しいエネルギー制約下では、通信速度がボトルネックになる」とAzita Emamiは、コメントしている。同氏は、電気工学、医療工学、Andrew and Peggy Cherng教授。電気工学役員、論文のシニアオーサ。

この課題に対処するためにCaltech/Southamptonチームは、最初から電子チップとフォトニックチップの両方を設計し、連係動作するようにそれらを最適化した。最初のアイデアからラボでの最終テストまでのプロセスは、完了までに4年かかった、全ての設計選択が、両方のチップに影響を与えからである。

「われわれは、システム全体を同時に最適化しなければならなかった。これは、優れた電力効率達成を可能にした。これら2-チップは、文字通り互いに作製され、互いに3次元に統合された」(Hashemi)。

結果として2つのチップ間の最適化されたインタフェースにより、送信ビット毎に2.4ピコジュールで、100Gbpsのデータを伝送できる。これは、現在の最先端技術と比較して、伝送の電子-光パワー効率を3.6倍改善する。ピコジュールは、1ジュールの1兆分の1、これは、1Ωの抵抗で1アンペアの電流により1秒に放出されるエネルギーとして定義されている。熱量は約0.24カロリー。

「世界がますます接続されるようになり、またあらゆるデバイスが生成するデータが増えると、従来の技術と比較してわずかなエネルギーを使いながら、そのような高データレートを達成できることを示すのは、実に素晴らしい」(Emami)。

論文タイトルは、”A 100Gb/s PAM4 Optical Transmitter in A 3D-Integrated SiPh-CMOS Platform Using Segmented MOSCAP Modulators.”

(詳細は、https://www.caltech.edu/)