Science/Research 詳細

Imecは、超低電力光I/O用ハイブリッドFinFET-SiPho技術を実証

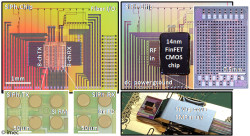

July, 12, 2018, Leuven--ベルギーの研究開発センターimecは、サン・フランシスコ(米国)で開催されているImec Technology Forum USAで、FinFET CMOS技術とシリコン・フォトニクスのハイブリッド集積による、超低消費電力、高帯域幅光トランシーバの実証を発表した。動的電力消費がわずか230fJ / bitで、フットプリントが0.025mm2であるため、40Gb/sのNRZ光トランシーバは、超高密度、マルチTb/s光I/Oを実現する重要なマイルストーンとなり、次世代のHPCアプリケーションに向けたソリューションを提供する。

データセンタースイッチやHPCノードで指数関数的に成長するI/O帯域需要が、光インタコネクトと先進的CMOSロジックの高密度集積要求を後押ししている。これらは、幅広いインタコネクト距離(1m~500m+)をカバーするものである。発表によると、差動FinFETドライバは、シリコンフォトニクスリング共振器とコデザインされ、154fJ/bitダイナミック消費電力で40Gb/s NRZ光変調を達成。レシーバは、Ge導波路フォトダイオードとの動作に最適化されたFinFETトランスインピーダンスアンプリファイア(TIA)を含んでおり、40Gb/s NRZフォトディテクションは、75fJ/bit消費電力で推定感度-10dBmが可能になっている。高品質データ伝送と受信も、1330nm波長、シングルモードファイバ(SMF)、リンクマージン2dB、ループバック実験で実証した。最後に、4×40Gb/s、0.1㎜2波長分割多重(WDM)トランスミッタ、温度制御組み込みを実証し、帯域100Gb/s/超ファイバが可能であることを示した。

「実証したハイブリッドFinFET – SiPhoプラットフォームに集積されているものは、高性能14nm FinFET CMOS回路、imecの300mm SiPho技術、デンス低容量Cuマイクロバンプ。この統合プラットフォームにおける慎重なコデザインにより、40Gb/s NRZ光トランシーバが可能になった。消費電力は著しく低く、高帯域密度であった」とImecの光I/O R&Dプログラムのディレクタ、Joris Van Campenhoutはコメントしている。さらに同氏は、「デザインの最適化により、短チャネルデータレートを56Gb/s NRZに高めることができると考えている。WDMと併用して、このトランシーバは、超コンパクト、マルチTb/s光インタコネクトにスケールするものであり、これは次世代ハイパフォーマンスシステムにとって重要である」と付け加えている。