Science/Research 詳細

エッジ端末に適した小型省電力プロセッサを実証

February, 25, 2021, 東京--東京工業大学 工学院 情報通信系の原祐子准教授らは、IoTの高度化において必要不可欠になる小型・省電力性を兼ね備えた新たなプロセッサを設計し、そのプロセッサの大規模集積回路(LSI)の開発に成功した。ヘルスケアデバイスを想定した異常検出においては、商用の最小プロセッサであるARM Cortex-M0の1.4倍高速でありながら電力効率は2.7倍、エネルギー効率は3.8倍を達成した。

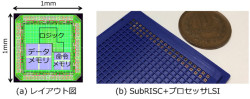

既存のプロセッサは多様化するアプリケーションのニーズに合わせ、大規模化と消費電力の増加が進んでいるため、小型デバイスのIoT化に対してはオーバースペックである。この研究では小型エッジ端末で必要な計算を実用的な時間で処理するための機能に限定することで、従来プロセッサに比べて回路面積を大幅に削減し、小型化と省電力化を両立するアーキテクチャ「SubRISC+」を開発した。65 nm CMOSプロセスを用いたプロセッサLSIは、1 mm×1 mmと小型、かつ、わずか77.0 µWの消費電力で、異常検出やデータ探索などの実用的なアプリケーションをリアルタイムに処理することができる。

開発したプロセッサは、原准教授らが2020年7月3日付で米国の科学誌「IEEE Access」に発表した研究成果を基に実機を試作し評価し、良好な結果が得られたものである。プロトタイプのサンプル配布も検討しており、今後はさらに用途の拡張と実用化を目指してチップの試作と開発を進めていく。

(詳細は、https://www.titech.ac.jp)